Types of CPU Organizations

The length of instruction depends on the CPU organization. There are four basic types of instructions in CPU Organization.

- Zero Address Instruction (Stack Organization)

- Single Address Instructions

- Two address instructions

- Three address instructions

Basic computers use single-address instructions. Let’s explain all of the above instructions. We will explain all these address instructions by using the following example

X= (a+b)*(c+d)

1. Zero Address Instruction (Stack Organization)

Zero address instructions have no operand with OPCODE.

Register Stack Organization Follow the Rule Last In First Out (LIFO).

Register Stack Organization Follow the Rule Last In First Out (LIFO).

- To insert data onto the stack, we use the PUSH command.

- To remove data from the stack, we use the POP command.

- Stack organization can be implemented on RAM or Registers.

EXAMPLE: Zero address instruction in register stack organization

Let’s explain X = (a+b)*(c+d) with Zero-address instructions

When we apply any OPCODE like ADD, MUL, etc., then it takes the previous two operands from the stack to apply the operation on them and stores the result in the position of the first operand. We cannot use any operand with OPCODE because it is a zero address instruction.

Implementation of registers as a stack

Mostly, 64 general registers are used for stack implementation, so 6 bits are required to address 64 registers.

- SP is a stack pointer (top of the stack) that stores the location’s address where we must push or pop any data. As SP stores the address of that location where we PUSH or POP data, its size will be 6 bits.

- Two flag registers named FULL and EMPTY are used.

- If the value of FULL is 1, then empty will be zero, and vice versa.

- If the FULL value is 1, then it means there is no more space to enter any new data.

- If the EMPTY value is 1, then it means we can add new data in stack-organized registers.

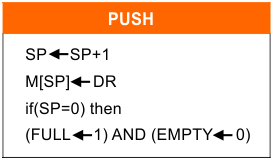

How to PUSH DATA?

As in the diagram, SP points to zero. When we want to add data from the data, register to the stack register.

- SP was incremented by 1, and points are the first general register addressing 1. If we want to add new data, then SP is incremented again, and data will be pushed to the second general register, and so on. This way, 63 (1 to 63) data values can be added to 64 general-purpose registers.

- When the 64th data value is added to the 64-register stack organization, SP points to ZERO because (64= 1000000). As the SP size is 6 bits, a higher bit is discarded, and the last 6 bits are considered. So, the SP value becomes (000000=0). When SP=0, FULL=1, and EMPTY=0, there is no more space to PUSH the 65th data value in the stack.

How to POP Data?

If we want to retrieve data from the stack to the Data Register, then we use the POP command. The memory location of the SP Address is POP and sends data to the Data Register. SP, decremented by 1. In the same way, the next memory location of the SP address is POP. We can remove more data from the stack until SP points to zero. When SP=0, then EMPTY =1 and FULL=0. It means all the stack is empty.

2. Single Address Instructions

It is also known as a Single Accumulator organization because OS uses a single operand. Here, the operand may be either the address of memory/ Register or maybe the data itself.

Format: Opcode + Address (Operand)

Let’s explain X = (a+b)*(c+d) with single-address instructions

This technique is entirely replaced by the introduction of the new general register.

Advantages of single address instructions

- One of the operands is always held by the accumulator register. This results in short instructions and less memory space.

- The Instruction cycle requires less time to complete

Disadvantages of single address instructions

- When complex expressions are executed, the program size will increase due to the execution of many short instructions.

- When the number of instructions increases for a program, then the execution time increases.

3. Two address Instructions

Two and three address instructions are considered as general register organizations.

- Two address instructions use two operands (1 source and another destination).

- More registers are required. So, More space is required for registers and buses. It is costly, but the speed is very high. But two address instruction speeds and costs are less than three address instructions.

- It is more costly than single-address instructions.

4. Three address instructions

- Three address instructions use three operands (2 sources and one destination).

- More registers are required to compare to zero, single, and two-address instructions. So, More space is required for registers and buses. That’s why it is more costly than other types of instruction.